锁相环技术入门简介

引言

设想一个问题:假如我手头有两个晶振,频率相同(比如都为32.768kHz),我们把这两个晶振激发出的时钟信号接到同一个示波器的两个端口,看到的波形会是相对静止的吗?

答案是不会,因为两个晶振虽然标定频率相同,但是都存在一定的误差,再加上外围匹配、温度漂移等条件的不同,就会使两个晶振的频率产生微小的差别。示波器按其中一个波形去固定触发时,另外一个波形就会相对移动。

同理,如果我们把两个不同的信号源设置到相同频率,接到同一个示波器上时,波形也会相对移动。如果我们把两个不同的DDS(直接数字频率合成器)输出的波形接到同一个示波器上时,波形也会相对移动。

这些现象是因为这些所谓的同频率信号并没有经过信号同步。

那么,如果有一个外面来的高频正弦波,我们希望输出一个与它完全同步的,相位差固定的(也就是说,在示波器上相对静止的)另一个正弦波,要怎么做呢?这就需要用到我们的锁相环(PLL,Phase Locked Loop)。

锁相环的基本构成

最基本的同步锁相环由两个关键部分组成:鉴相器(PD,Phase Detector)和压控振荡器(VCO,Voltage Controlled Oscillator)。

鉴相器

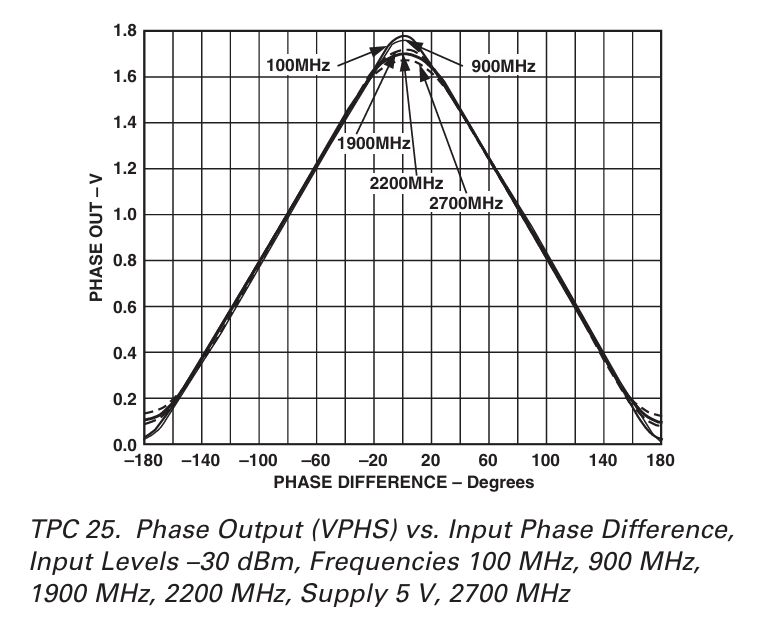

鉴相器,顾名思义,就是鉴定相位差的一种器件,输入两个(通常是高频)信号,输出一个电压值,输出电压值与两个输入信号的相位差相关。

如图所示,这是AD8307鉴相器的输出特性曲线,可以看到在输入的两个信号相位差为0时,输出电压最高达到约1.8V,而在输入的两个信号相位差为±180°时,输出电压最低达到约0V。

压控振荡器

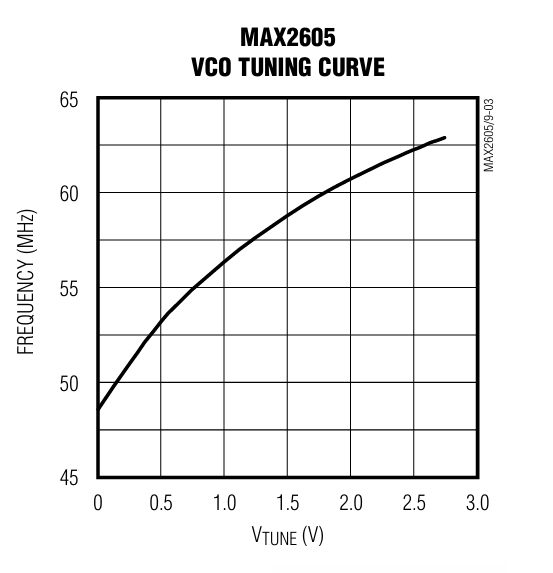

压控振荡器就是用电压控制的振荡器,输入一个电压值,输出一个高频正弦波,且输出频率与输入电压值相关。

如图所示,这是MAX2605压控振荡器的输出特性曲线,可以看到输入电压从0V增长到3V时,输出频率从大约48MHz增长到大约63MHz。

为什么锁相环能同步信号

锁相环的结构很简单,只要把PD的输出接到VCO的输入,把VCO的输入和外部信号分别接到PD的两个输入,就是一个最简单的锁相环了。

当output与input的频率完全相同时,它们之间的相位差也会是一个固定值,于是VCO的输出频率不会改变,让output的频率与input继续保持相同;而当output与input的频率不相同时,它们之间的相位差也不固定,那么PD的输出就是一个变化的值,这会导致VCO的输出也随之改变。output与input的频率差越大,PD输出变化越快,VCO输出频率变化越快;output与input的频率差越小,PD输出变化越慢,VCO输出频率变化越慢,相当于“精细调整”。

经过这一系列负反馈的调节,output的频率会锁定在与input完全相同的频率上,在示波器上可观察到相对静止的波形。

稳定性改进

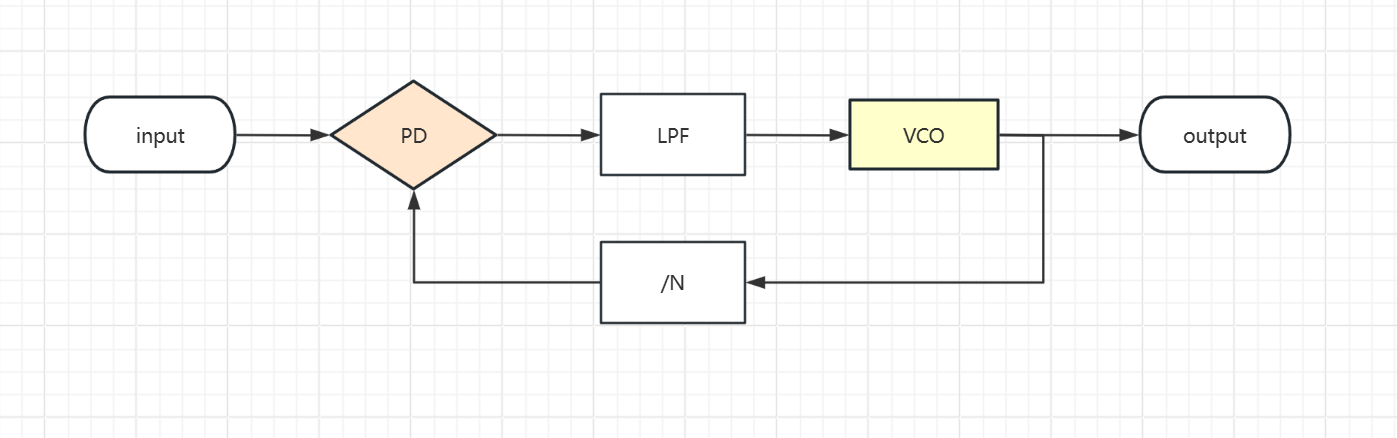

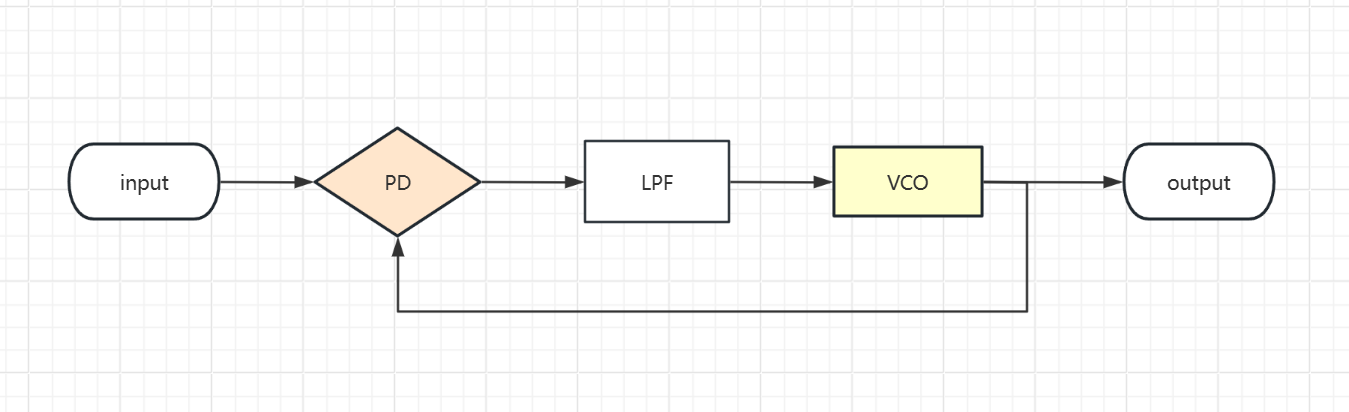

上面提到的是最简单最基本的理论锁相环结构,事实上为了拥有一个稳定的锁相环,还需要在PD输出和VCO输入之间插入一个低通滤波器(LPF,Low Pass Filter),相当于对频率变化做一个缓冲,使锁相环更容易锁定住,而不是飘来飘去,结构如下图所示。

倍频锁相环

锁相环的一大实际应用就是用作倍频器。普通的STM32芯片也能跑到大几十甚至几百MHz的频率,但是它们所使用的晶振却一般没有那么高的频率,这就是因为这些MCU内部集成了内部的PLL模块,可以把外部的晶振给出的相对较低频的时钟信号倍频为更高频的时钟信号。

上面我们介绍过的基本锁相环输出的信号是严格与输入信号同频率的。怎么输出倍频呢?

分频器

分频器是一个数字电路模块,输出频率为输入频率的整数分之一倍,通常比较常见的简单的分频器是二的幂次分频。这也很好理解,比如每次输入信号经过一个周期,就将输出信号的极性翻转,这样就已经是一个最简单的二分频器了;将两个二分频器进行串联,就可以得到四分频器。

将分频器应用于锁相环

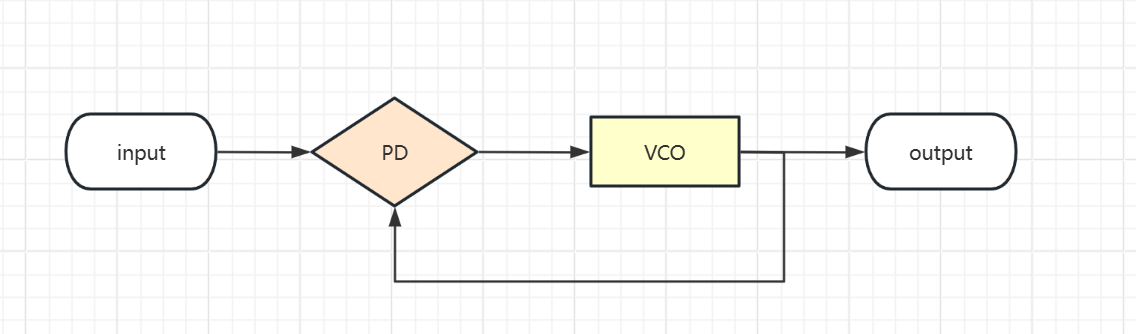

现在我们希望在PLL中输出信号的频率是输入信号频率的倍数,那么如果反过来看,也就是希望输入信号是输出信号频率的整数分之一倍,也就是说,希望输出信号经过分配器之后,与输入信号进行同步,这样就可以达到输出信号为输入信号频率倍数的目的。

如果用“/N”来表示一个N分频器,那么N倍频PLL的结构就可以如下表示: